سلام به همه همراهان اسمارت کامپ! امیدواریم حالتون خوب باشه. در این مقاله، شما را با تراشه فلیپ فلاپ JK با تکنولوژی TTL به شماره 74LS76 آشنا خواهیم کرد.

74LS76 دارای ورودی های J، K مجزا، پالس ساعت، ورودی پاک کردن و نشاندن به منطق یک (set) مستقیم است. این فلیپ فلاپها بهگونهای توسعه مییابند که وقتی کلاک در حالت HIGH قرار میگیرد، دادهها دریافت میشوند و ورودیها را فعال میسازند.

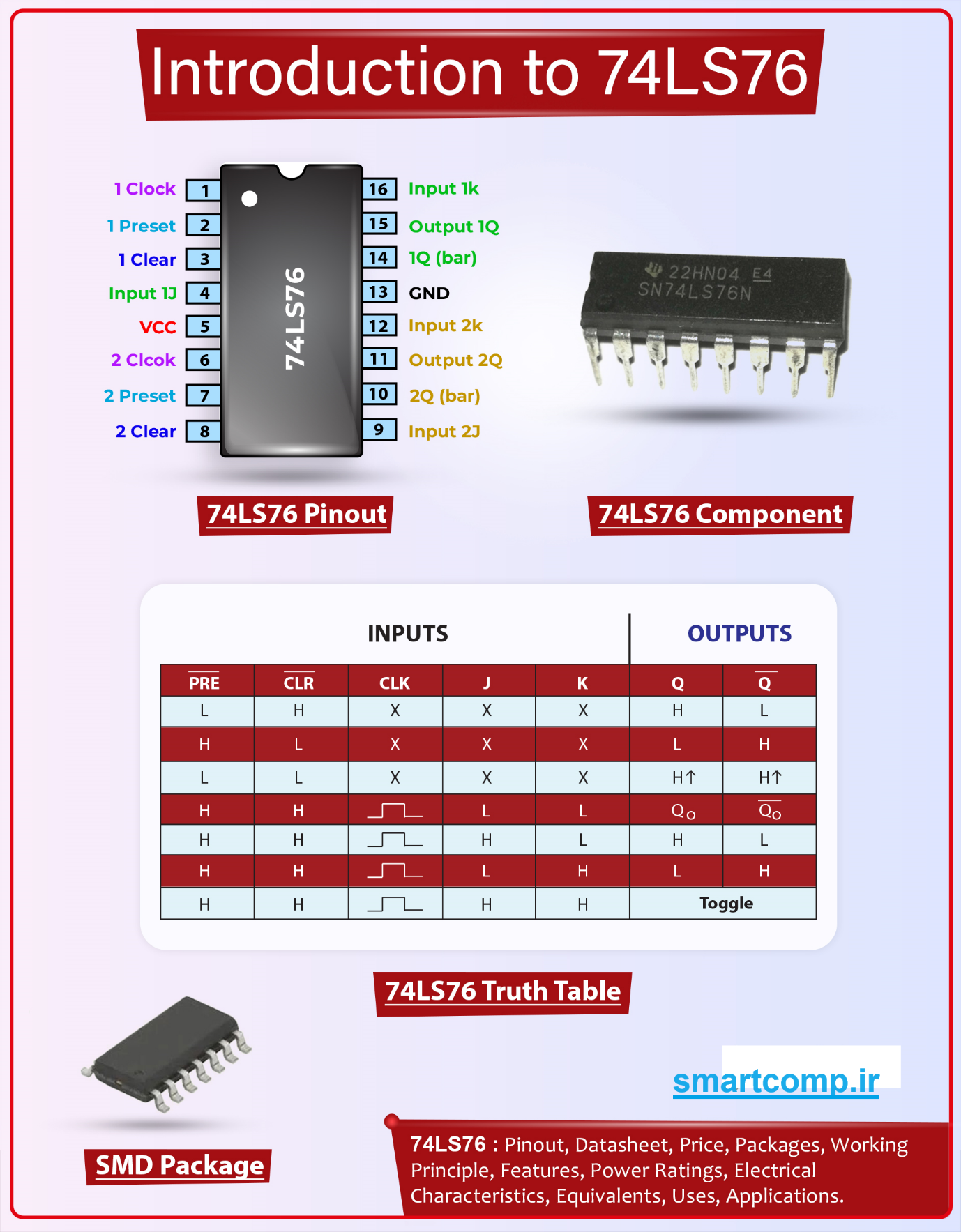

مقدمه ای بر 74LS76

74LS76 دارای ورودی های J، K مجزا، پالس ساعت، ورودی پاک کردن و نشاندن به منطق یک (set) مستقیم است. این فلیپ فلاپها بهگونهای توسعه مییابند که وقتی کلاک در حالت HIGH قرار میگیرد، دادهها دریافت میشوند و ورودیها را فعال میسازند.

این آی سی شامل دو فلیپ فلاپ JK است و هر فلیپ فلاپ را می توان به صورت جداگانه برای کاربردهای مورد نیاز استفاده کرد.

این فلیپ فلاپها عمدتاً در رجیسترهای کنترل، شیفت رجیسترها و رجیسترهای ذخیرهسازی به کار میروند و به دلیل توانایی آنها در به خاطر سپردن تک تک بیتهای داده، به عنوان دستگاههای لچکننده نامیده میشوند.

این قطعات الکترونیکی بر اساس داده های باینری ذخیره شده، خروجی را قفل می کنند.

توجه به این نکته مهم است که بیش از یک فلیپ فلاپ را می توان به صورت سری برای ذخیره مقدار کمی داده به عنوان EEPROM ترکیب کرد.

محدوده ولتاژ کاری این فلیپ فلاپ دو تایی JK 2 تا 6 ولت است و در بسته های 14 پین PDIP، GDIP و PDSO عرضه می شود.

این فلیپ فلاپ JK بهترین انتخاب برای کاربردهای عملی نامیده می شود زیرا دارای خروجی پایدار برای همه انواع ورودی است.

سطوح منطقی ورودیهای J و K تا زمانی که حداقل زمان تنظیم در نظر گرفته شود، مطابق جدول درستی انجام میشود.

بدانید که داده های ورودی زمانی به خروجی تبدیل می شوند که انتقال کلاک از HIGH به LOW رخ می دهد.

این آی سی دو فلیپ فلاپ JK را در خود جای داده و از +5 ولت تغذیه می کند.

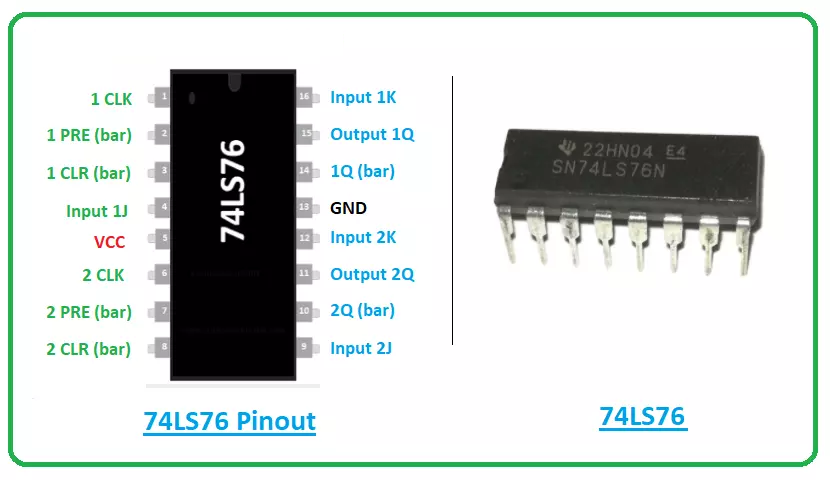

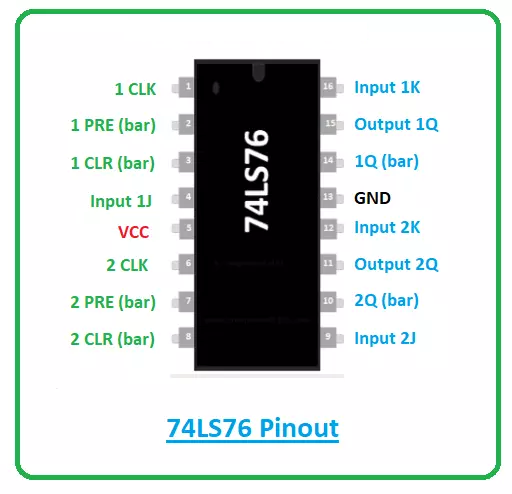

پایه های 74LS76

در زیر نمودار پایه های 74LS76 آمده است.

جدول زیر شرح پایه های تراشه 74LS76 را نشان می دهد.

| Pin Description of 74LS76 Dual JK Flip-Flop | ||||

| Pin No. | Pin Description | Pin Name | ||

| 1,6 | These pins should be provided with a clock pulse for the flip flop | Clock-1/ Clock-2 | ||

| 2,7 | Preset input pins drive Flip Flop to a set state. | Preset-1 / Preset-2 | ||

| 16,12 | Input pin of the Flip Flop | 1K/ 2K | ||

| 4,9 | Another Input pin of the Flip Flop | 1J / 2J | ||

| 14,10 | The inverted output pin of Flip Flop | 1Q(bar) / 2Q (bar) | ||

| 15,11 | Output Pin of the Flip Flop | 1Q / 2Q | ||

| 3,8 | Clear input pin drives Flip Flop to a reset state. | 1 CLR (bar)/ 2 CLR (bar) | ||

| 13 | Connected to the ground | Ground | ||

| 5 | Powers the IC with 5V | Power (+Vs) | ||

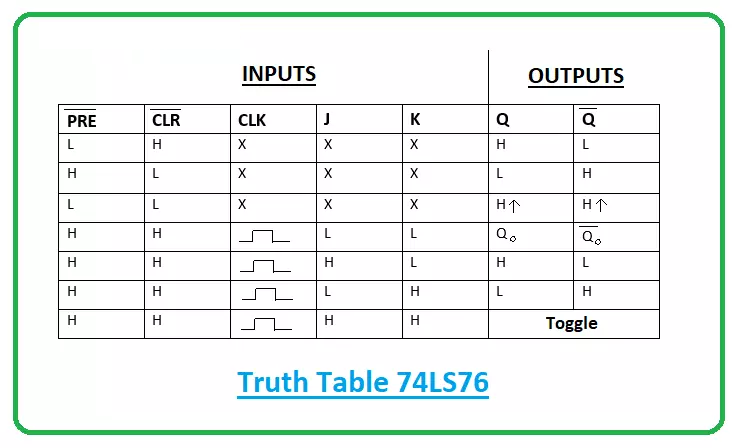

جدول درستی 74LS76

clear و از preset به عنوان ورودی های فعال-پایین ناهمزمان نامگذاری شده اند. هنگامی که آنها به LOW تنظیم می شوند، منجر به نادیده گرفتن J-K می شوند و ورودی های کلاک اجازه می دهند خروجی در سطوح حالت پایدار باقی بماند. جدول درستی 74LS76 در زیر نشان داده شده است.

ویژگی های 74LS76

ویژگی های اصلی تراشه در زیر توضیح داده شده است.

محدوده ولتاژ کاری = 2 ولت تا 6 ولت

حداکثر ولتاژ خروجی سطح پایین = 0.25 ولت

حداقل ولتاژ خروجی سطح بالا = 3.5 ولت

دو عدد فلیپ فلاپ مستقل JK

محدوده دمای عملیاتی = -55 تا -125 درجه سانتیگراد

حداکثر ولتاژ ورودی سطح پایین = 0.8 V

حداقل ولتاژ ورودی سطح بالا = 2 ولت

بسته های موجود = PDIP 14 پین، GDIP، PDSO

کاربردهای 74LS76

در زیر کاربردهای اصلی فلیپ فلاپ 74LS76 آورده شده است.

در رجیسترهای حافظه/کنترل استفاده می شود

در شیفت رجیسترها استفاده می شود

برای عملیات لچ کردن (نگهداری) داده ها استفاده می شود.

در مدارهای EEPROM گنجانده شده است

دیدگاه خود را بنویسید